# 工學碩士 學位論文

# 소형 3-dB 브랜치 라인 결합기를 이용한 고출력 평형 증폭기 설계

Design of High Power Balanced Amplifier Using Branch Line Coupler in Reduced Type

指導教授 姜 仁 鎬

2003年 2月

韓國海洋大學校 大學院

電波工學科

鄭 秉 九

# 목 차

| Abstract ·····                                             |     |

|------------------------------------------------------------|-----|

| Nomenclature ·····                                         | ii  |

|                                                            |     |

| 제 1 장 서 론                                                  | 1   |

|                                                            |     |

| 제 2 장 브랜치 라인 결합기의 설계 이론                                    | 3   |

|                                                            |     |

| 2.1 임피던스 변환 결합기                                            | 3   |

| 2.2 소형 임피던스 변환 결합기                                         | 8   |

| 2.3 각 포트에서 임의의 종단 임피던스를 갖는 결합기                             | 15  |

| 2.4 결합 선로를 이용한 초소형\/4 전송선로 ·····                           | 19  |

|                                                            |     |

| 제 3 장 평형증폭기의 설계                                            | 25  |

|                                                            |     |

| 3.1 전력 이득                                                  |     |

| 3.2 안정성                                                    |     |

| 3.3 고주파 전력 증폭소자의 특성                                        |     |

| 3.4 고주파 전력 증폭소자의 선택                                        |     |

| 3.5 평형증폭기                                                  | 34  |

|                                                            |     |

| 제 4 장 측정 및 결과 분석                                           | 36  |

| 4.1 실험에 사용된 전력 증폭기의 특성                                     | 200 |

| 4.1 실임에 사용된 선덕 등록기의 특성 ··································· |     |

| 4.2 세식 夫 설립                                                | 31  |

| 제 5 장 결 론                                                  | 41  |

| 씨 U ő 결 〒 ······                                           | 41  |

| J -                                                        |     |

| 참고 문헌                                                      |     |

### **Abstract**

The hybrid coupler plays an important role in microwave circuits such as balanced mixers, image-rejection mixers, and balanced amplifier. Among them, the balanced amplifier is used for the mismatched power amplifier. However, the balanced amplifier may still be mismatched at both path of two equal amplifier because the power TR has low input-output impedance.

Besides of it the standard balanced amplifier configuration has the disadvantage requiring a large space owing to the coupler's size. The method of applying arbitrary lumped-distributed impedance transforming couplers to balanced amplifiers significantly reduces the size of over the conventional balanced amplifier with 50  $\Omega$  input/output couplers. then, the size of arbitrary lumped-distributed impedance transforming couplers tend to be restricted by the characteristic impedance.

In order to solve the above problem, in this thesis, design graphs were drawn for the reduced size coupler, which was terminated by arbitrary impedances and shorted coupled-line pair. The coupler size was 90 percent smaller than the conventional coupler.

A balanced amplifier was designed using the coupler with shorted coupled-line pair and lumped capacitor. The measured gain is  $6 \pm 0.2$  dB, the input and output VSWR are lower than 1.40.

# Nomenclature

G : 전력이득

K : 트랜지스터의 안정지수

P<sub>d</sub> : 전력손실

Pi : 입력 전력

T : 저항의 잡음온도 (Kelvin, °K)

Te : 우모드 여진 투과 계수

T。 : 기모드 여진 투과 계수

$Z_L$  : 부하 임피던스

$Z_{in}$  : 입력 임피던스

$Z_0$  : 특성 임피던스

$Z_{out}$  : 출력 임피던스

$Z_S$  : 소스 임피던스

$\Gamma_e$  : 우모드 여진 반사 계수

$\Gamma_o$  : 기모드 여진 반사 계수

$\Gamma_{\it OUT}$  : 출력 반사 계수

$\Gamma_S$  : 소스 반사 계수

△ : 델타지수

arepsilon : 유전율

$\theta_{J\!C}$  : 열저항

# 제 1 장 서 론

최근 이용량이 급증하고 있는 무선 통신의 비약적인 발전으로 무선통신 회로 및 부품을 직접화, 소형화, 안정화는 현재 마이크로파 및 밀리미터파 회로에서 주로 사용되는 결합기의 경우 평형 증폭기(balanced amplifiers)나 평형 혼합기(balanced mixer)등과 같은 초고주파 회로에서 중요한 역할을 하고 있으며, 또한 MMIC (monolithic microwave integrated circuit)나 MIC (microwave integrated circuit)에 같은 회로에서도 매우 중요한 소자이다.

일반적으로 고출력 증폭기의 경우 매우 낮은 입·출력 임피던스를 가지게 되는데 이렇게 낮은 임피던스를 정합 하여 증폭기를 제작할 경우 입·출력의 부정합 문제를 발생시켜 증폭기의 안정성을 위협하고, 이득을 감소시킨다.

이런 문제를 해결하기 위해 대표적으로 평형 증폭기가 사용되어 진다. 평형 증폭기를 사용할 경우 높은 안정성과 2배의 출력 파워, 한 쪽의 파손 시에도 사용 가능하다는 이점등이 있다. 하지만 평형증폭기는 결합기를 사용하기 때문 에 일반적으로 크기가 매우 크다는 단점이 발생한다.

그러나 최근 결합기를 커패시터 소자와 분포 정수 회로를 이용해 크기를 줄이면서 증폭기의 낮은 임피던스에 부합할 수 있는 소형 임피던스 변환 결합기가 제안되었다. 하지만 이 결합기는 낮은 종단 임피던스에 의해 비대칭 구조를 가지게 되고 이로 인해 문제점이 발생하였다.

본 논문에서는 비대칭 구조에서 발생하는 문제점을 해결하기 위해 모든 종단의 임피던스를 변화시킨 결합기를 제안하였다. 이 제안된 결합기를 이용해서 평형증폭기를 설계할 경우 기존의 크기를 줄인 임피던스 변환 결합기를 이용한 평형증폭기에 비해 크기를 더욱 작게 구현 할 수 있다. 또한 직접회로 제작시결합기에서 발생하는 손실을 줄일 수 있는 장점도 생긴다. 또한 커패시터 소자와 분포 정수 회로로 구성된 소형 결합기보다 더욱 소형화된 병렬 결합선로를 이용한 결합기도 제안하였다.

본 논문의 2장에서는 결합기의 설계 및 해석 방법에 대해 설명하고, 3장에서 는 평형 증폭기를 설계하기 위한 증폭기 설계 이론과 평형 증폭기의 구조에 대 해 설명하고, 4장에서는 ADS 설계 tool을 이용한 시뮬레이션과 실제 제작 후 측정된 평형 증폭기의 측정 결과에 대한 분석을 하였다.

# 제 2 장 브랜치 라인 결합기의 설계 이론

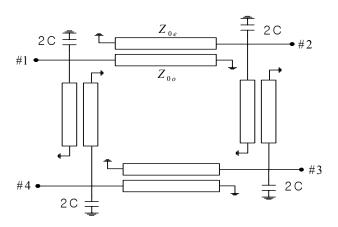

## 2.1 임피던스 변환 결합기

마이크로파 소자로 널리 쓰이고 있는 3-dB 브랜치 라인 결합기(이하, 동의어 "결합기, 브랜치 라인 결합기, 브랜치 라인 하이브리드"라 함)는 평형 증폭기 (balanced amplifiers)나 평형 혼합기(balanced mixer)등과 같은 여러 회로에서도 자주 쓰이고 있다. 이 때 전력 증폭기는 높은 전력을 내기 위해 높은 전류를 수용해야 해야 하는데 이로 인해 낮은 입력 임피던스와 출력 임피던스를 가진다. 때문에 이 경우에는 종단 임피던스가 낮은 임피던스로 변환된 결합기가요구된다.

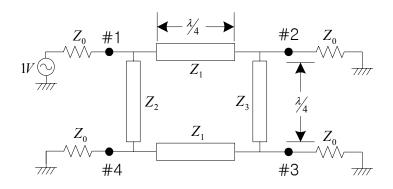

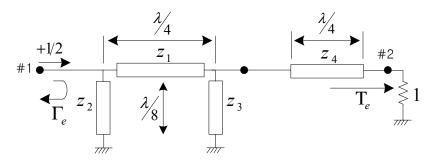

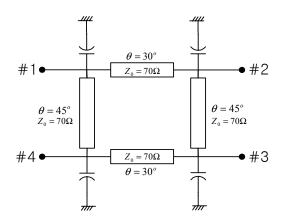

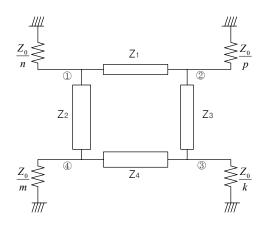

그림 2.1은 일반적인 결합기의 구조이다. #1은 포트 1(입력), #2는 포트 2(출력), #3는 포트 3(출력), #4는 포트 4(격리)이다. 그림 2.1은 종단 임피던스가 모두 같은 경우이다. 여기서 포트 2와 포트 3가 임의의 종단 임피던스를 가지면 그림 2.2 (a)와 같이 나타낼 수 있다. 그리고 그림 2.2의 결합기는 AA'축을 중심으로 대칭이며, 가역적인 소자이다.

그림 2.1 결합기의 구조

Fig. 2.1 Configuration of branch-line coupler.

그림 2.2 임의의 대칭형 종단 임피던스를 갖는 결합기

Fig. 2.2 Symmetric coupler terminated by arbitrary impedances.

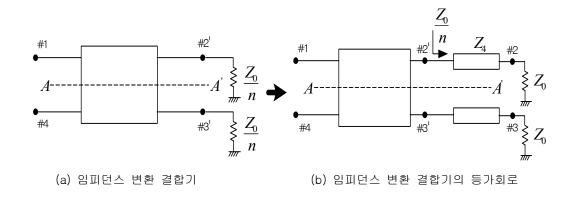

그림 2.2의 (b)의 회로에서 특성 임피던스가  $Z_4$ 인  $\lambda/4$  전송선을 사용한 이유는 #2', #3'에서 우측 회로로 보았을 때  $Z_0/n$ 로 될 수 있도록 만든 회로이다. 이경우  $Z_4=Z_0/\sqrt{n}$ 가 된다. 그림 2.3은 그림 2.2의 회로를  $Z_0$ 로 정규화한 회로이며,  $Z_1$ ,  $Z_2$ ,  $Z_3$ ,  $Z_4$ 는 정규화된 특성 임피던스이다. 다음에서 임의의 종단 임피던스를 가지는 3-dB 브랜치 라인 결합기를 우·기모드(even·odd mode) 해석 방법으로 해석하였다.

그림 2.3 임의의 종단 임피던스를 갖는 결합기의 정규화된 회로 Fig. 2.3 The normalized circuit of coupler terminated by arbitrary impedances.

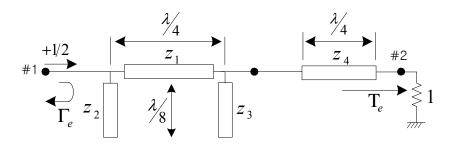

#### (1) 우모드 해석

그림 2.4 우모드 여진시의 등가회로

Fig. 2.4 Equivalent circuit for even-mode excitation.

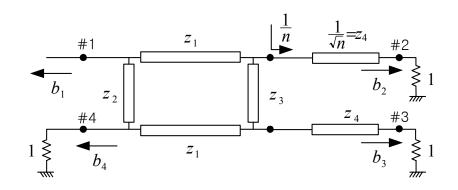

그림 2.4는 그림 2.3의 회로에서 포트 1과 4에 입력 전압을 각각 1/2씩 인가하였을 때 최종회로이다. 그림 2.4에서 특성 임피던스가  $z_2$  , $z_1$  , $z_3$  , $z_4$ 인 회로이다. 여기서  $y_1 = \frac{1}{z_1}$ ,  $y_2 = \frac{1}{z_2}$ ,  $y_3 = \frac{1}{z_3}$ ,  $y_4 = \frac{1}{z_4}$ 이며,  $\beta = \frac{2\pi}{\lambda}$ 이므로  $l = \frac{\lambda}{4}$ 이면  $\beta = \frac{\pi}{2}$ 가 되어 포트 1에서 포트 2까지의 ABCD 파라미터를 정리하면 식 (2.1)과 같다.

$$\begin{bmatrix} A_e & B_e \\ C_e & D_e \end{bmatrix} = \begin{bmatrix} -z_1 y_4 & -jz_1 y_3 z_4 \\ -jz_1 y_2 y_4 & -y_1 z_4 + z_1 y_2 y_3 z_4 \end{bmatrix}$$

(2.1)

## (2) 기모드 해석

그림 2.5는 그림 2.3의 회로에서 포트 1과 4에 각각 1/2, -1/2씩 전압을 인가하였을 때 최종회로이다. 그림 2.5에서 특성 임피던스가  $z_2$ ,  $z_1$ ,  $z_3$ ,  $z_4$ 인 회로이다.

그림 2.5 기모드 여진시의 등가회로

Fig. 2.5 Equivalent circuit for odd-mode excitation.

여기서

$$y_1 = \frac{1}{z_1}$$

,  $y_2 = \frac{1}{z_2}$ ,  $y_3 = \frac{1}{z_3}$ ,  $y_4 = \frac{1}{z_4}$ 이며,  $\beta = \frac{2\pi}{\lambda}$ 이므로  $l = \frac{\lambda}{4}$ 이면  $\beta = \frac{\pi}{2}$ 가 되어 포트 1에서 포트 2까지의 ABCD 파라미터를 정리하면 식  $(2.2)$ 와 같다.

$$\begin{bmatrix} A_{o} & B_{o} \\ C_{o} & D_{o} \end{bmatrix} = \begin{bmatrix} -z_{1}y_{4} & jz_{1}y_{3}z_{4} \\ jz_{1}y_{2}y_{4} & -y_{1}z_{4} + z_{1}y_{2}y_{3}z_{4} \end{bmatrix}$$

(2.2)

식 (2.1)과 식 (2.2)를 비교하면, 우모드와 기모드의 ABCD 파라미터 관계는 다음과 같다.

$$A_e = A_o, B_e = -B_o, C_e = -C_o, D_e = D_o$$

(2.3)

이 두 포트에 대한 입력파의 진폭은 각각 우모드일 때 +1/2, +1/2이고, 기모드일 때 +1/2, -1/2이므로, 가지선로 하이브리드의 각 포트에 나타나는 파의 진폭은 다음과 같이 정의된다.

$$b_{1} = \frac{1}{2} \Gamma_{e} + \frac{1}{2} \Gamma_{o} = S_{11} \qquad b_{2} = \frac{1}{2} T_{e} + \frac{1}{2} T_{o} = S_{21}$$

$$b_{3} = \frac{1}{2} T_{e} - \frac{1}{2} T_{o} = S_{31} \qquad b_{4} = \frac{1}{2} \Gamma_{e} - \frac{1}{2} \Gamma_{o} = S_{41}$$

$$(2.4)$$

반사와 전송계수에 등가인 S파라미터로 ABCD 파라미터를 전환하면 다음과 같이 나타낼 수 있다.

$$\Gamma_{e} = \frac{A_{e} + B_{e} - C_{e} - D_{e}}{A_{e} + B_{e} + C_{e} + D_{e}} \qquad T_{e} = \frac{2}{A_{e} + B_{e} + C_{e} + D_{e}}$$

$$T_{o} = \frac{2}{A_{o} + B_{o} + C_{o} + D_{o}} \qquad \Gamma_{o} = \frac{A_{o} + B_{o} - C_{o} - D_{o}}{A_{o} + B_{o} + C_{o} + D_{o}}$$

(2.5)

최종적으로 식 (2.2), 식 (2.3)및 식 (2.5)를 이용하고,

$S_{11}=0$ ,  $S_{21}=-\frac{1}{\sqrt{2}}$ ,  $S_{31}=\frac{j}{\sqrt{2}}$ ,  $S_{41}=0$  조건으로부터 식 (2.6)과 식 (2.7)을 얻을 수 있다.

$$y_1^2 = 2 y_3$$

(2.6)

$$y_3^2 - 2ny_3 + n^2 = 0 (2.7)$$

위의 식 (2.6)과 식 (2.7)을 풀면 각 선로의 정규화된 임피던스는 다음과 같다.

$$y_3 = n \tag{2.8}$$

$$y_1 = \sqrt{2n} \tag{2.9}$$

그림 2.6 1/n로 정규화된 종단 임피던스를 갖는 결합기 Fig. 2.6 The coupler with normalized load impedances by 1/n.

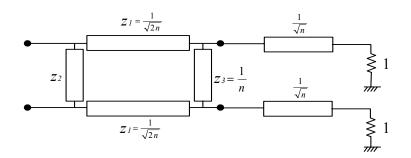

따라서, 종단 임피던스가  $\frac{Z_0}{n}$ 인 회로를 정상적인 방향성 결합기로 이용할 경우 그림 2.6과 같이 정규화된 임피던스로 나타낼 수 있다.

## 2.2 소형 임피던스 변환 결합기

T. Hirota에 의해 기존의 결합기에 비해 크기를 줄인 결합기가 제안되었다 [2]. 기존의  $\lambda/4$  결합기를 소형화시키는 방법으로 높은 임피던스를 가지는 전송선로와 병렬 커패시터의 조합으로 구현하였고, 이 방법으로 기존의 결합기에 비해 크기를 80 %까지 작게 설계가 되었다. T. Hirota에 의하면 일반 전송선로는 인덕턴스와 커패시턴스 성분으로 이루어져 있다. 이럴 경우 전송 선로의 길이를 줄일 경우 커패시턴스 성분과 인덕턴스 성분이 작아 지게 되는데 작아진 커패시턴스 성분을 병렬로 커패시터 소자를 부가하여 커패시턴스 값을 보정하고 인덕턴스의 손실 부분은 특성 임피던스를 증가시키므로 해서 길이가 짧아지는 문제를 보상 할 수 있다.

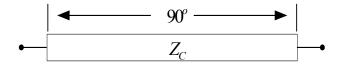

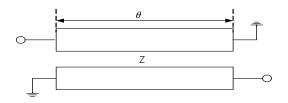

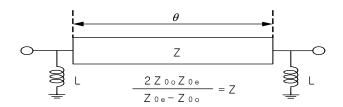

먼저 그림 2.7에서 N/4 전송선로의 ABCD 매트릭스는 식 (2.10)과 같다.

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 0 & jZ_c \\ j/Z_c & 0 \end{bmatrix}$$

(2.10)

그림 2.7 λ/4 전송선

Fig. 2.7 Quarter-wave transmission section.

그림 2.8 크기가 줄어든  $\lambda/4$  전송선 등가회로

Fig. 2.8 Reduced-size circuit equivalent to quarter-wave section.

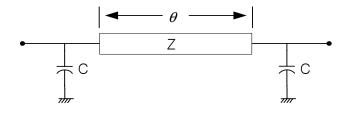

$\lambda/4$  전송선은 그림 2.8에서 보여진 형태로 변환 될 수 있다. 여기서 Z는 특성임피던스,  $\theta$ 는 전기적 길이, C는 병렬 커패시턴스 이다. 여기서  $Z>Z_C$  일 때전기적 길이  $\theta$ 가  $90^\circ$ 보다 작아진다.

그림 2.8에서 전송선로의 ABCD 매트릭스는 식 (2.11)과 같이 나타낼 수 있다.

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cos \theta - \omega C Z \sin \theta & j Z \sin \theta \\ j \frac{\sin \theta}{Z} + 2j\omega C \cos \theta - j(\omega C)^{2} Z \sin \theta & \cos \theta - \omega C Z \sin \theta \end{bmatrix}$$

(2.11)

식 (2.10)과 식 (2.11)을 이용해서 다음과 같이 구할 수 있다.

$$Z = \frac{Z_c}{\sin \theta} \tag{2.12}$$

$$\omega C = \frac{\cos \theta}{Z_c} \tag{2.13}$$

위의 결과식에 의해 일반적인  $\lambda/4$  브랜치 라인 결합기와 크기를 줄인 전송 선의 관계식을 볼 수 있다. 위의 식을 이용하여 일반적인 결합기를 크기를 줄 인 결합기로 변환하면 그림 2.9와 같으며, 본 논문에서는 소형화된 결합기라고 한다.

그림 2.9 소형화된 결합기 회로

Fig. 2.9 Circuit of the reduced-size coupler.

35  $\Omega$ 을 70  $\Omega$ 으로 변환할 경우  $Z/Z_c$ 의 값은 2,  $\sin\theta=1/2$ 이고  $\theta=30$  °가 되고, 50  $\Omega$ 을 70  $\Omega$ 으로 변환할 경우  $Z/Z_c$ 의 값은 $\sqrt{2}$ ,  $\sin\theta=1/\sqrt{2}$ 이고  $\theta=45$  °가 된다. 이 경우 기존의 결합기보다 80 %이상 작아지는 장점을 가지고 있다.

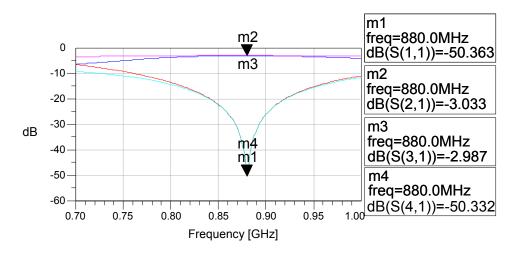

그림 2.10 소형화된 결합기의 주파수 특성 Fig. 2.10 Frequency characteristic of the reduced-size coupler.

그림 2.10은 소형화된 결합기를 시뮬레이션한 결과이며, 이것은 기존의  $\lambda/4$  결합기보다는 대역폭이 줄어드는 단점을 가지고 있다.

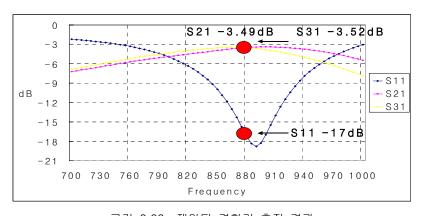

그림 2.11 소형화된 결합기의 측정 결과 Fig. 2.11 Measured result of reduced-size coupler.

그림 2.11은 소형화된 결합기를 제작 측정한 결과이다. 그러나, 측정결과에서 손실 부분은 커패시터의 정확한 용량치가 일치하는지 또는 제작 고정에서 오차인지 불분명하다.

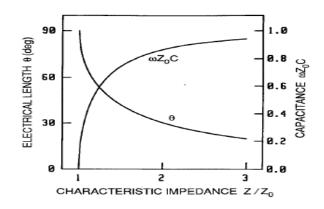

그림 2.12는  $Z/Z_c$ 의 비에 따른 전기적 길이  $\theta$ 와의 관계를 보여 주고 있다. 여기서  $Z/Z_c$  비가 2를 넘을 경우 전기적 길이  $\theta$ 가 약 1/3정도로 줄어드는 것을 볼 수 있다.

그림 2.12 줄어든 전송 선로의 등가 조건 Fig 2.12 Equivalent condition of the shortened transmission line[2].

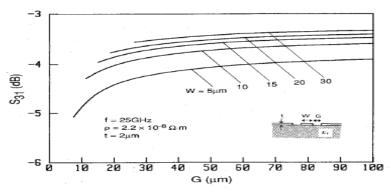

그림 2.13 CPW의 간격 G에 따른 25GHz에서 소형화된 결합기의 선로 폭에 따른 삽입손실 Fig. 2.13 Calculated insertion losses of the 25 GHz reduced size coupler as a function of conductor gap G of the coplanar waveguide[2].

그림 2.13은 T. Hirota에 의해 제안된 소형화된 결합기에서 전송선로의 폭

W와 삽입손실의 관계를 나타낸 그림이다.

T. Hirota의 이론을 적용하면 N/4 전송선로의 길이를 줄일수록 전송선로의 특성 임피던스는 높아지며, 특성 임피던스가 높아지면 선로의 폭 W가 감소한다. 즉 전송선로의 폭을 어느 정도 이하로 줄이게 되면 삽입 손실 특성이 나쁘게 나타나는 것을 볼 수 있는데, 이것은 conductor loss에 의해 야기된다. 그리고 특성 임피던스가 어느 정도 이상으로 증가하면 전송 선로로 구현하기가 어려울 정도로 선로의 폭이 급격하게 줄어들게 될 뿐만 아니라, 줄어든 폭로 인하여 선로의 삽입 손실도 증가하게 된다는 문제점이 발생하는 것을 알 수 있다. T. Hirota에 의해 제안된 결합기의 경우 크기를 줄이는 데에는 한계가 있음을 보여준다.

하지만 이런 문제점은 보통의 낮은 입·출력 임피던스를 가지는 증폭기와 결합하는 평형증폭기 경우 기존의 소형화된 결합기보다 더 작은 크기를 구현할수 있는 장점이 생긴다. 이 구조는 앞에서 언급한 임의의 낮은 종단 임피던스를 가질 경우, Zc을 낮게 하는 효과를 가지기 때문에 기존의 경우 보다 더 짧은 λ/4 전송선을 구현할 수 있다.

그림 2.14 소형화된 임피던스 변환 결합기 회로

Fig. 2.14 The Circuit of the impedance-transforming reduced-size coupler.

그림 2.14는 이와 같은 원리를 이용하여 낮은 임피던스에 종단된 포트에는 낮은 특성 임피던스를 갖는 효과로 인해  $\lambda/4$  전송선이 더욱 줄어드는 경향을 나타내는 회로이다.

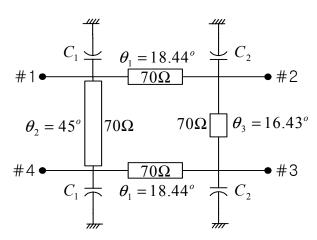

만약 포트 2, 3의 종단 임피던스가 20  $\Omega$ 인 결합기를 설계할 경우  $Z_2$ 의 경우 50  $\Omega$ 으로,  $Z_1$ 은 22.36  $\Omega$ ,  $Z_3$ 는 20  $\Omega$ 으로 변환된다. 그림 2.14에서 결합기의 각선로의 임피던스를 70  $\Omega$ 으로 변화시켜서 설계를 하면 다음과 같다. 전기적 길이  $\theta_1$ =18.44°,  $\theta_2$ =45°,  $\theta_3$ =16.43°이고,  $C_1$ ,  $C_2$ 는 각각 10.2 pF, 16.4 pF으로 나타났다. 그림 2.14에서 T. Hirota가 제안한 결합기보다  $\theta_1$ 은 2.44배,  $\theta_3$ 는 2.7배 정도로 작아지는 것을 볼 수 있다. 이럴 경우 기존의 소형화된 결합기보다 더 작은 크기를 구현 할 수 있다는 장점이 생긴다.

하지만 소형화된 임피던스 변환 결합기의 경우  $\theta_2$ 가  $\theta_3$ 에 비해 50 %이상 커지는 단점이 발생한다. 대부분의  $Z/Z_c$  비율의 차이에서도  $\theta_2$ 가  $\theta_3$ 에 비해 많은 차이가 난다. 이런 문제점을  $Z_2$ 의 임피던스를 가지는 선로의 구조적 변형에 의해 크기를 줄일 수는 있지만 전체적으로 크기에 증가를 가져온다. 그리고 포트 2와 3의 종단 임피던스가 작아지면 작아 질수록  $Z_2$ 와  $Z_3$ 의 임피던스를 가지는 선로의 길이 비율의 차이가 많이 나는 문제점을 가지게 된다. 그렇게 되면 전체적으로 설계하는데 문제점이 발생한다[3].

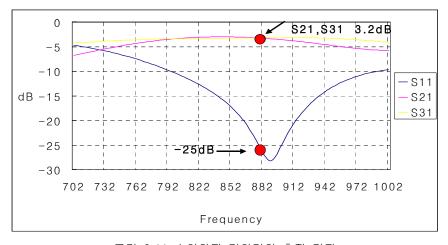

그림 2.15 소형화된 임피던스 변환 결합기의 주파수 특성

Fig. 2.15 Frequency characteristic of the impedance-transforming reduced-size coupler.

그림 2.16 20Ω 임피던스 변환 소형 결합기의 측정 결과

Fig. 2.16 Measured result of 20  $\Omega$  impedance-transforming reduced-size coupler.

그리고 그림 2.15는 시뮬레이션 결과로 소형화된 임피던스 변환 결합기의 주 파수 특성을 나타내고 있다.

그림 2.16은 20 Q 임피던스 변환 소형 결합기를 제작 측정한 결과이다. 측정 결과 약간의 손실이 발생하였다.

# 2.3 각 포트에서 임의의 종단 임피던스를 갖는 결합기

그림 2.17 임의의 종단 임피던스를 갖는 결합기

Fig. 2.17 The coupler terminated by arbitrary impedances.

그림 2.18 임의의 종단 임피던스를 갖는 결합기의 등가회로

Fig. 2.18 The Equivalent circuit of coupler terminated by arbitrary impedances.

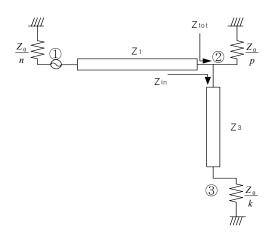

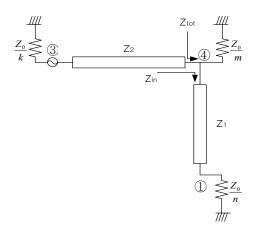

그림 2.17은 모든 포트가 임의의 종단 임피던스를 갖는 브랜치 라인 결합기를 나타낸다. 여기서 종단 임피던스가 다르기 때문에 대칭성이 존재하지 않으므로 일반적인 해석방법이 적용되지 않는다. 모든 포트의 종단 임피던스가 다른 경우의 커플러가 Ahn에 의해 다음과 같이 제안되었으며,  $Z_1$ ,  $Z_2$ ,  $Z_3$ ,  $Z_4$ 의 임피던스는 다음과 같이 구해진다[4],[5].

그림 2.18은 포트 ①은 여기 시키고 포트 ④가 격리일 경우 그에 해당하는 등가 회로이다. 그림 2.18은 3 dB 결합기이므로  $Z_{in}$ 은 ③의 종단 임피던스와 같은 임피던스를 가져야 한다. 그러므로 ②의 종단 임피던스와 ③의 종단임피던스는 1/4 임피던스 변환기 역할을 하므로 임피던스 1/4 임기단스 본다.

$$Z_{3} = \sqrt{\frac{Z_{o}}{p} \cdot \frac{Z_{o}}{k}} = \sqrt{\frac{1}{p \cdot k}} \cdot Z_{o} \tag{2.14}$$

그리고 그림 2.18에서  $Z_{tot}$ 는  $Z_0/p$ 와  $Z_{in}$ 의 병렬연결이므로  $Z_{tot}$ = $Z_0/2p$ 가 된다. 그러므로 임피던스  $Z_1$ 은 다음과 같다.

$$Z_{1} = \sqrt{\frac{Z_{o}}{2n} \cdot \frac{Z_{o}}{p}} = \sqrt{\frac{1}{2n \cdot p}} \cdot Z_{o}$$

(2.15)

그림 2.19 임의의 종단 임피던스를 갖는 결합기의 등가회로

Fig. 2.19 The Equivalent circuit of coupler terminated by arbitrary impedances.

위와 같은 방법으로 반대쪽을 해석하면, Z<sub>2</sub>의 임피던스는 식 (2.16)과 같다.

$$Z_{2} = \sqrt{\frac{Z_{o}}{m} \cdot \frac{Z_{o}}{n}} = \sqrt{\frac{1}{m \cdot n}} \cdot Z_{o} \tag{2.16}$$

그림 2.19에서  $Z_{tot}$ 는  $Z_0/m$ 과  $Z_{in}$ 의 병렬연결이므로  $Z_{tot}$ = $Z_0/2m$ 가 된다. 그러므로 임피던스  $Z_4$ 는 식 (2.17)과 같다.

$$Z_4 = \sqrt{\frac{Z_o}{2m} \cdot \frac{Z_o}{k}} = \sqrt{\frac{1}{2m \cdot k}} \cdot Z_o \tag{2.17}$$

이렇게 하여 각 종단에 다른 임피던스를 가지는 결합기를 제작할 수 있다.

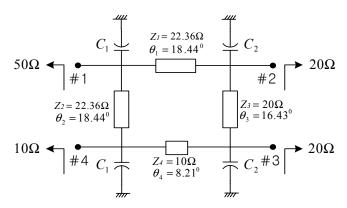

본 논문에서는 그림 2.14에서와 같이  $Z_2$ ,  $Z_3$ 의 비대칭 구조에서 발생하는 문제점을 해결하는 방법으로 다음과 같이 제안하였다.

전기적 길이  $\theta_2$ 를 줄이는 방법으로 포트 4의 종단 임피던스를 변화시키는 방법을 택하였다. 포트 4의 종단 임피던스를 변화시킬 경우 임의의 특성 임피던스로 변환이 가능하다. 만약 포트 2와 3의 종단 임피던스가  $20\ \Omega$ 이 될 경우, 포트 4의 임피던스를  $10\ \Omega$ 으로 변화시켜 종단시킬 경우 제안된 결합기의 각

임피던스 및 전기적 길이 8는 그림 2.20에서 보여지는 것과 같다.

그림 2.20 임의의 임피던스에 종단된 소형 결합기 회로

Fig. 2.20 The circuit of reduced-size coupler terminated by arbitrary impedances.

그림 2.20에서 알 수 있는 바와 같이 포트 4의 종단 임피던스를 조절함으로 써  $\theta_2$ 의 전기적 길이를 변화시킬 수 있게 되었고, 이로 인해  $\theta_2$ 와  $\theta_3$ 의 비대 청에서 오는 문제점을 해결할 수 있어 기존의 소형화된 임피던스 변환 결합기보다 전체적으로 크기를 줄일 수 있는 장점을 가지고 있다. 또한 특성 임피던스가 낮아짐으로 해서 그림 2.13에서 보는 것처럼 선로의 폭을 크게 할 수 있어 성능이 개선시킬 수 있는 장점도 가지고 있어 직접회로 제작시에 크기와 성능면에서 개선된 회로 제작이 가능해진다. 그림 2.21은 시뮬레이션 결과를 나타내고 있다.

그림 2.21 임의의 임피던스에 종단된 결합기의 주파수 특성

Fig. 2.21 Frequency characteristic of coupler terminated by arbitrary impedances.

그림 2.22 제안된 결합기 측정 결과 Fig. 2.22 Measured result of proposed coupler.

그림 2.22는 본 논문에서 제안한 포트 4의 임피던스를 변환한 결합기의 측정 결과이다.

실험실에서 사용하는 커패시터의 소자의 경우 소수점 이하의 정확한 값을 가지고 있지 못하기 때문에 본 논문에서 제안한 결합기의 경우 정확하게 -3 dB로 분배가 되지 못하고 손실이 많이 발생하였다. 이것은 설계상 각 선로의 임피던스가 틀리기 때문에 커패시턴스의 값을 모두 다르게 설계가 되어야 한다. 앞에서 설계된 Hirota에 의해 제안된 결합기의 경우 커패시터는 하나의 커패시턴스 값을 가지고, 임피던스 변환 결합기의 경우 2개의 커패시턴스 값을 가지며, 본 논문에서 제안한 모든 종단 임피던스가 다른 결합기의 경우 4개의 다른 커패시턴스 값을 가진다. 그렇기 때문에 그림 2.11, 그림 2.16, 그림 2.22를 비교할 경우 손실이 점점 더 많이 발생하는 것을 볼 수 있다.

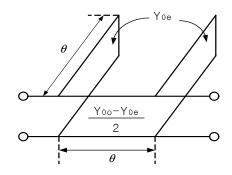

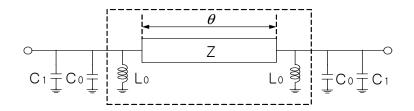

# 2.4 결합 선로를 이용한 초소형 λ/4 전송선로

Hirota에 의해 제안된 결합기의 경우 인덕터를 사용하지 않고  $\lambda/4$ 전송선로의 크기를 줄일 수 있는 방법을 제시하고 있지만, 소형화 및 IC화 되어가는 방향성 결합기의 최근 추세로 볼 때 만족스러울 만큼의 소형화를 이루어내고 있지 못하다. 그래서 본 논문에서는 이런 문제점을 해결하기 위해서  $\lambda/4$  전송선

로에 분기된 커패시터를 갖는 끝부분이 단락된 병렬 결합 전송선로로 구현함으로써  $\lambda/4$  전송선로 보다 작게 설계 할 수 있는 방법을 제시한다.

그림 2.23 병렬 결합 전송선로 Fig. 2.23 Shorted coupled-line pair.

그림 2.24 병렬 결합 전송선로의 등가회로

Fig. 2.24 The equivalent circuit of shorted coupled-line pair.

그림 2.25 병렬 결합 선로의 등가회로

Fig. 2.25 The lumped equivalent circuit of shorted coupled-line pair.

그림 2.23과 그림 2.24는 모든 주파수에 대하여 등가적으로 사용할 수 있다[6]. 여기서, 그림 2.24에 도시된 단락 선로는 그림 2.22와 같이 인덕터로 표현할 수 있으며, 이 경우 인덕턴스 값은 식 (2.18)으로 표현될 수 있다.

$$L = \frac{Z_{0e} \tan \theta}{\omega} \tag{2.18}$$

그림 2.23과 같이 병렬 결합 선로를 사용하는 이유는  $Z=\frac{2~Z_{0o}~Z_{0e}}{Z_{0e}-Z_{0o}}$ 의 식에 서  $Z_{0e}$ ,  $Z_{0o}$ 를 조절하면 매우 높은 특성 임피던스를 도출할 수 있기 때문이다.

그림 2.26 소형화된 λ/4 전송선 등가회로

Fig. 2.26 Reduced-size circuit equivalent to quarter wave section.

그림 2.27 공진 회로를 부가한 소형화된 전송선로

Fig. 2.27 The artificial resonant circuit is inserted in the reduced-size line.

그림 2.26은 2.2절에서 설명된 방법에 의해  $\lambda/4$ 전송선로를 소형화시킨 아주 높

은 특성 임피던스를 갖는 회로라고 가정한다. 이것은 그림 2.25에서 매우 높은 특성 임피던스 Z을 갖는 회로를 그림 2.26의 회로에 연결시키기 위하여 그림 2.27과 같이 커패시터를 부가하여 인위적으로 공진을 시킨다(여기서,  $C_0$ 와  $L_0$ 는 중심 주파수에서 공진한다고 가정). 이렇게 하면 인덕터를 사용하지 않고 구현할 수 있다. 이 때  $C_0$ 는  $\omega_0 C = \frac{1}{\omega_0 L}$ 과 같이 나타낼 수 있다.

그림 2.28  $\lambda/4$  전송 선로의 최종 등가회로 Fig. 2.28 The final equivalent  $\lambda/4$  transmission line circuit.

그렇게 되면 최종적으로 그림 2.26에 도시된 아주 높은 임피던스를 갖는 소형화된 전송선로는 그림 2.28에 도시된 것과 같이 분기된(shunt) 커패시터를 갖는 끝부분이 단락된 병렬 결합 전송선로로 구성될 수 있다.

그림 2.28에 도시된  $\lambda/4$  전송선로를 소형화시킨 전송선로는 높은 특성 임피 던스를 갖고 있으며 인덕터를 사용하고 있지 않음을 알 수 있다.

그림 2.29는 매우 짧은  $\lambda/4$  전송선 결과식을 이용하여 나타낸 방향성 결합 기이다. 실제 제작 결과 결합기 제작시 병렬 결합 선로로만 이루어지기 때문에 Hirota에 의해 제안된 결합기에 비해 크기를 줄일 수 있는 장점이 생긴다.

그림 2.29 병렬 결합 전송 선로 결합기 Fig. 2.29 Shorted coupled-line pair coupler.

예로 880 MHz에서 모든 종단 임피던스가 50  $\Omega$ 인 일반 결합기를 설계를 할경우 과정을 살펴보면 그림 2.26에서 Z의 임피던스를 150  $\Omega$ 이상 높여서  $\theta$  값과 C값을 구할 수 있다. 이때  $\theta$  값은  $10^\circ$ 이하로 줄어들게 된다. 그리고 커플드라인의 넓이 W는 커플링 계수 K를 임의로 정하여  $Z_{0e}$ 와  $Z_{0o}$ 를 구하게 된다. 결과적으로 Hirota가 제안한 소형 N/4 전송선 보다 더 작게 설계가 가능한 것을알 수 있다. 여기서 커플링 계수 K는 다음과 같이 정의된다.

$$K = \frac{Z_{0e} - Z_{0o}}{Z_{0e} + Z_{0o}}$$

예로 일반적인 결합기를 커플드라인을 이용한 결합기로 변형하면 다음과 같다. 특성 임피던스를 214  $\Omega$ 이고,  $Z_{0e}$ =94.6  $\Omega$ ,  $Z_{0o}$ =50.2  $\Omega$ 이고 유전율  $\epsilon_r$ =3.5, 높이 h=0.51 mm인 테프론 기판으로 설계할 경우이다. 35  $\Omega$ 은 전기적 길이  $\theta$ =9.49°이고, 전송선의 폭은 W=0.5 mm, 커패시터 C=14.4 pF, 결합선로 사이 간격 S=0.2 mm, 커플링 계수 K=-10.28 이었다. 50  $\Omega$ 은 전기적 길이  $\theta$ =13.5°이고, 전송선의 폭 W=0.5 mm, 커패시터 C=10.17 pF, 결합 선로 사이 간격 S=0.2 mm, 커플링 계수 K=-10.28 이었다.

위의 경우에도 결합기의 특성 임피던스가 낮으면 전기적 길이 θ가 더 작아

지는 것을 알 수 있다.

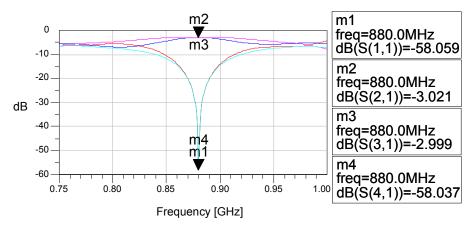

그림 2.30 병렬 결합선로를 이용한 결합기의 주파수 특성

Fig. 2.30 Frequency characteristic of shorted coupled line pair coupler.

그림 2.31 병렬 결합선로를 이용한 결합기의 측정 결과

Fig. 2.31 Measured result of shorted coupled line pair coupler.

그림 2.30은 병렬 결합 선로를 이용하여 시뮬레이션한 결과이고, 그림 2.31은 병렬 결합 선로를 이용한 결합기의 측정 결과이다. 중심 주파수가 약 20 MHz 이동 한 것을 볼 수 있는데, 이 결합기 또한 정확한 커패시터 소자를 사용하기에 힘든점과 병렬 결합기 사이의 좁은 간격, 그리고 접지에서 오는 문제등 실험상의 부정확성 때문이다.

## 제 3장 전력 증폭기의 설계

#### 3.1 전력이득

증폭기 설계시 중요한 것은 이득, 안정도, 대역폭, 입·출력 정재파비등 중요한 요소들이 있다.

이득 및 안정도는 증폭기 설계시 매우 중요하게 생각되어져야 하는 요소로서 s-parameter, matching network 등에 의해서 결정된다.

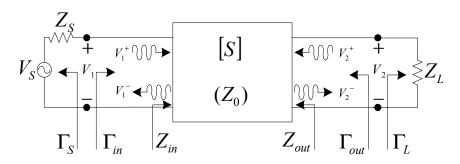

그림 3.1 일반적인 2-포트 회로망 Fig. 3.1 Two-port network.

위의 그림에서 [S]-matrix를 가지는 2포트 회로망에  $Z_S$ ,  $Z_L$  임피던스를 가지게되면 다음과 같이 3가지의 전력이득으로 표시할 수 있다.

동작전력 이득(operating power gain)  $G_{p}$ 는 다음과 같이 정의된다

$$G_p = \frac{$$

부하에 공급되는 전력  $}{$  회로망의 입력에 공급된 전력  $} = \frac{P_L}{P_{in}}$

회로의 입력단자에 power가 전달되어 부하단에 power가 소모되는 비율이다. (여기서의 이득은  $Z_s$ 에 독립적이다.)

가용 전력 이득(available gain)  $G_A$ 는 다음과 같이 정의된다.

$$G_A = rac{$$

회로망으로부터 가용할 수 있는 전력  $}{$  부하에 공급할 수 있는 최대전력  $} = rac{P_{avn}}{P_{avn}}$

회로망에서 가용할 수 있는 전력  $P_{AV\!N}$ 과 부하에 공급할 수 있는 최대전력  $P_{AV\!N}$  와의 비율이다.

변환 전력 이득(transducer power gain)  $G_T$ 는 아래와 같이 정의된다.

$$G_T = \frac{$$

부하에 공급되는 전력  $}{$  전원으로부터의 가용전력  $}= \frac{P_L}{P_{qqq}}$

신호원으로부터 가용할 수 있는 전력  $P_{AVS}$ 는 회로망에 공급할 수 있는 최대 전력이다.

여기서 two-port회로에 만약 입력과 출력이 모두 정합되면 이득은 최고가 되며  $G_P = G_A = G_T$  가 된다.

$G_{P}$ ,  $G_{A}$ ,  $G_{T}$ 를 정의하기 위해 다음과 같이 구할 수 있는데, 먼저 입출력 반사계수를 정의하면 다음과 같다.

$$\Gamma_{i} = \frac{Z_{i} - Z_{0}}{Z_{i} + Z_{0}}$$

(i=L, S)

$V_1$  전압은 식 (3.1)과 같다.

$$V_{1} = V_{s} \frac{Z_{in}}{Z_{s} + Z_{in}} = V_{1}^{+} + V_{1}^{-} = V_{1}^{+}(1 + \Gamma_{in})$$

(3.1)

식 (3.1)을  $Z_{in}$ 에 대해 풀고,  $V_{1}^{+}$ 에 관해서 풀면 다음과 같다.

$$V_1^+ = \frac{V_s(1 - \Gamma_S)}{2(1 - \Gamma_S \Gamma_{in})} \tag{3.2}$$

다음은 이득을 구하기 위해서 식 (3.2)을 이용해  $P_{in}$ 을 구하면, 여기서  $P_{in}$ 의 값은 회로로 전달되는 평균전력이다.

$$P_{in} = \frac{1}{2Z_0} |V_1^+|^2 (1 - |\Gamma_{in}|^2) = \frac{V_s^2}{8Z_0} \frac{(1 - \Gamma_s)^2}{(1 - \Gamma_s \Gamma_{in})^2} (1 - \Gamma_{in}^2)$$

(3.3)

$P_{T}$ 은 부하에 전달되는 평균전력으로 식 (3.4)로 나타낼 수 있다.

$$P_{L} = \frac{|V_{2}^{-}|^{2}}{2Z_{0}} (1 - |\Gamma_{L}|^{2})$$

(3.4)

식 (3.3)과, 식 (3.4)을 이용하여  $G_p$ 를 구하면 다음과 같다.

$$G_{P} = \frac{P_{L}}{P_{in}} = \frac{|S_{2l}|^{2} (1 - |\Gamma_{L}|^{2})}{(1 - |\Gamma_{in}|^{2})|1 - S_{22} \Gamma_{L}|^{2}}$$

(3.5)

$P_{avs}$  은 회로로 전달되는 최대 전력이며, 이 전력은 입력 임피던스와 소스임피던스의 공액 복소수가 같을 때 얻을 수 있는 전력이다. 이것은 식 (3.6)과 같이 나타낼 수 있다.

$$P_{avs} = P_{in} \quad (\Gamma_L = \Gamma_{S^*}) \tag{3.6}$$

P ..... 은 부하에 전달되어지는 최대전력이다.

$$P_{avn} = P_L \qquad (\Gamma_L = \Gamma_{out^*}) \tag{3.7}$$

이렇게 하여 GA와 GT를 구하면 다음과 같다.

$$G_{A} = \frac{P_{avn}}{P_{avs}} = \frac{|S_{21}|^{2}(1 - |\Gamma_{S}|^{2})}{|1 - S_{11}|\Gamma_{S}|^{2}(1 - |\Gamma_{out}|^{2})}$$

(3.8)

$$G_T = \frac{P_L}{P_{avs}} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|1 - \Gamma_S \Gamma_{in}|^2 |1 - S_{22} \Gamma_L|^2}$$

(3.9)

# 3.2 안정성(Stability)

증폭기 설계시 안정도는 매우 중요하다. 2-포트회로에서 발진은 입력이나 출력측 임피던스가 부저항 성질을 가질 때 발생한다, 즉  $|\Gamma_{IN}|>1$  이나  $|\Gamma_{OUT}|>1$  일 때 경우에 나타나므로 이 조건으로부터 안정 조건을 구할 수 있다. 무조건 안정의 조건은 증폭회로에서 소스 반사계수  $\Gamma_S$ 와 부하 반사 계수  $\Gamma_L$ , 그리고 입력과 출력 반사계수  $\Gamma_{IN}$ ,  $\Gamma_{OUT}$ 은 다음과 같은 조건을 만족할 때 안정한 동작을 한다 .

$$\mid \Gamma_{S} \mid <1 \tag{3.10}$$

$$\mid \Gamma_L \mid <1 \tag{3.11}$$

$$|\Gamma_{IN}| = \left|S_{11} + \frac{S_{12} S_{21} \Gamma_L}{1 - S_{22} \Gamma_S}\right| < 1 \tag{3.12}$$

$$|\Gamma_{OUT}| = \left|S_{22} + \frac{S_{12} S_{21} \Gamma_L}{1 - S_{11} \Gamma_S}\right| < 1$$

(3.13)

무조건 안전성은 K 와  $\triangle$ (Delta factor)를 통해 알 수 있는데, 다음과 같이 정의된다. (Rollet's condition)

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 |\Delta|^2}{2|S_{12}S_{21}|} > 1 \tag{3.14}$$

$$|\Delta| = |S_{11} S_{22} - S_{12} S_{21}| < 1 \tag{3.15}$$

그러므로 무조건 안정조건은 K>1 ,  $|\triangle|<1$  즉, S-parameter가 이 조건을 만족하지 않으면 무조건안정영역이 아니다[7].

## 3.3 고주파 전력 증폭소자의 특성

# 3.3.1 고주파 전력 소자의 직류 특성

# (1) 항복전압

고주파 트랜지스터 선택에 있어서 가장 민감한 부분은 항복전압으로 증폭기의 바이어스 전압과 밀접한 관계가 있다. 응용분야에 따라 보통 6 V, 9 V,  $2 \text{ 4} \sim 50 \text{ V}$  사이의 고전압을 사용하기도 한다.

### (2) 누설전류

고주파 트랜지스터의 내부에서 애벌런치 항복전압에서 발생되는 역바이어스의 접합전류로 정의되는 누설전류는 반도체 물질의 결함, 마스크의 불안전성 또는 웨이퍼 처리 과정에서 원하지 않는 불순물의 투입 등에 의하여 나타나며, 누설전류의 제한점 등을 고려하여 고주파소자를 선택하여야 한다.

#### (3) 전력손실

고주파 트랜지스터에서의 전력손실은 열저항( $\theta_{JC}$ )과 밀접한 관계가 있다. 최대 전력손실은 실제적으로 트랜지스터의 케이스 온도가  $25\,^{\circ}C$ 로 유지한다는 가정에 의한 값이므로, 증폭기가 출력전력에서 동작하는 동안 반도체 소자의 케이스는 온도변화가 발생하게 되는데, 이때의 온도 변화에 따라 열저항을 측정하므로 다음과 같은 식에 의하여 계산되어진다.

$$\theta_{JC} = (T_J - T_C)/(P_{in} - P_0)$$

$$P_d = (T_{Jmax} - 25 \, {}^{\circ}C)/\theta_{JC}$$

여기서,  $T_c$ 는 반도체 소자의 케이스 온도,  $T_J$ 는 접합온도,  $P_{in}$ 은 입력전력,  $P_o$ 은 출력전력이다.

## 3.3.2 고주파 전력 소자의 교류 특성

전력용 고주파 트랜지스터의 선택은 동작 주파수, 출력전력, 이득 및 동작전 압에 따라 이루어진다. 이러한 전력용 고주파 트랜지스터의 동작 특성은 이득, 반사전력, 효율 및 부하 변동 유지능력 등으로 나타낼 수 있으며, 특성을 측정하기 위해서는 반도체 제조회사에서 제시하는 측정기법을 도입해야 한다.

#### (1) 부하 변동 유지 능력

전력용 고주파 트랜지스터의 교류(AC)특성에서 변동 부하 유지능력이 매우 중요한 파라미터이다. 변동 부하 유지 능력은 부하 값이 변하여 부정합 상태에서 트랜지스터의 동작 능력 또는 신뢰성의 변화 없이 얼마나 특성을 잘 유지하는가를 의미한다. 여러 가지 회로 조건, 즉 위성 통신단말기에 대하여 안테나에의한 전력 트랜지스터의 임피던스 값의 변화에는 제한이 있다. 그러므로 고주파 트랜지스터는 안테나의 파손이나 안테나의 존재 유무와 같은 부하의 부정합에 대하여도 지속적인 동작에 아무런 영향을 주진 않고 그 성능을 나타낼 수 있어야 한다. 이러한 변동 부하 유지능력 시험 후에도 고주파 전력 트랜지스터가 아무런 변화 없이 동작해야 하므로 제조 회사에서는 부하 변동 유지능력을 정재파비 (VSWR)가 2:1에서 30:1까지의 범위에서 부하의 부정합에 대한 입력과 출력전력의 관계를 트랜지스터의 자료에 명시하고 있다.

## (2) 고주파 전력용 트랜지스터의 대신호 입출력 임피던스

고주파 전력용 트랜지스터의 입출력 단의 임피던스 정합 방법은 저잡음 증폭기의 임피던스 정합 방법과는 달리 전력 트랜지스터의 입, 출력 임피던스( $Z_{in}$ ,  $Z_{out}$ )값을 측정하여 정합회로를 설계한다. 전력 트랜지스터의 입, 출력 임피던스 값의 측정은 여러 가지 방법이 있지만 일반적으로 제조회사에서 대신호 임피던스 파라미터를 제공해 주고 있다. 이 값은 스미스 도표(smith chart)상에 주파수에 대한 임피던스 값의 변화를 나타내거나 도표로 수치 값이 주어진다. 그리고 다른 방법으로, load-pull 방식에 의한 입, 출력 임피던스의 측정은 벡터 회로망 분석기에 의하여 회로의 반사계수를 측정하며, 이 때 DUT (Device Under Test)가 최대 전력을 갖도록 조정한 후 short방식 또는 adapter방식을 가지고 측정한다[8],[9].

#### 3.4 고주파 전력 증폭소자의 선택

고출력 전력증폭 시스템을 설계함에 있어서 우선 고려되어야 할 사항은 고출력 레벨과 저출력 레벨로 구분하여 고주파 신호를 증폭시키는 전력소자의 선택에 있다. 이러한 전력용 능동 소자는 최종 출력단의 설계 규격에 적합한 소자를 선택해야 하며, 일반적으로 고출력 쌍극성 트랜지스터(BJT)와 전계 효과 트랜지스터(FET)가 사용되고 있다.

#### (1) 저출력 고주파 트랜지스터의 선택

저출력 트랜지스터의 선정 방법은 설계 목적과 응용에 따라 달라진다. 저잡음 증폭기의 경우 고주파 트랜지스터의 선택은 사용주파수와 잡음지수 등을 고려해야 하며, 대부분의 경우에 있어서 제조 회사에서 사용주파수에 따른 잡음파라미터(최소 잡음지수, 잡음 저항성과 최소 잡음지수의 저항원)와 바이어스조건 등을 제공해 준다.

저출력 트랜지스터는 거의 유사한 항복전압을 갖고 있기 때문에 고출력증폭기의 소자에 비해 비교적 간단하게 선정할 수 있으며, 저출력 증폭기의 설계에 있어서 설계목적에 알맞은 전류비와 충분히 큰 차단주파수를 갖는 소자를 선정해야 설계 목적에 맞는 동작주파수 범위에서 원하는 이득을 얻을 수 있다. 특히 저출력 고주파 트랜지스터 선정에 있어서 먼저 고려해야 할 사항은 트랜지스터의 패키지 형태이다. 금속 캔(metal can), Plastic SOE(Stripline Opposed Emitter), 표면 장착(surface mount)형태가 있으며, 고주파 트랜지스터의 경우패키지를 적게 할수록 기생 효과는 작게 나타나므로 능동 소자의 고주파 성능이 우수하게 나타나고 경제성 있는 패키지를 고려해야 한다.

#### (2) 고출력 고주파 트랜지스터의 선택

수 W 이상이 고출력 고주파 트랜지스터 경우, 선택의 폭이 비교적 작기 때문에 고출력 소자의 선정에는 출력전력, 동작전압 및 주파수를 고려하여 선정

되어야 한다. 특히 고출력 고주파 트랜지스터에서 필연적으로 고려되어야 할 사항은 직선성, 대역폭, 효율, 부하 변동 유지능력 및 열적 안정이 필요 조건이 다. 동작전압의 경우 설계시에 미리 설정되므로 낮은 공급전원과 높은 공급전 원의 사용에 따른 장단점을 고려해야 한다. 이 경우에 있어서 고출력 고주파 트랜지스터의 입력 임피던스의 정합 방법에 대하여 큰 변화는 없으나, 출력 임 피던스는 동작전압과 출력전력 레벨에 따라 변화되므로 가능한 설계시에 부하 임피던스에 임피던스 변환에 의한 정합 회로를 설계할 수 있도록 동작전압을 설계해야 한다. 다단 증폭 시스템의 설계에 있어서 구동단(driver stage)이나 전치구동단(predriver stage)은 최종 출력단에 비하여 비교적 낮은 전원전압을 사용하며 다음단의 입력 임피던스와 정합을 쉽게 하도록 해야 한다. 동작주파 수 관점에서 고주파 트랜지스터의 선택은 쉽게 할 수 있으며, 이때 증폭 소자 의 안정도, 부하 변동 유지능력과 경제성이 고려되어야 한다. 고출력 고주파 트 랜지스터 제조 회사에서는 비교적 낮은 입력 임피던스와 고출력을 위한 동작점 을 경감시키고자 능동 소자 패키지 내부에 정합회로(internal matching)를 형성 시켜 트랜지스터의 임피던스 값을 크게 하며, 또 임피던스 값을 변화시켜 리액 턴스 성분을 감소시킴으로써 동작점을 저하시키기도 한다. 이와 같은 내부 정 합회로를 갖는 고주파 트랜지스터를 선정함으로서 설계 목적에 맞는 대역폭 문 제를 해결할 수 있다. 고출력 증폭 시스템이 설계에 있어서 증폭기의 효율과 선형성은 바이어스 회로와 정합회로 설계에 따라 결정되므로 이러한 관계를 고 려하여 증폭기 시스템을 설계해야 한다[10].

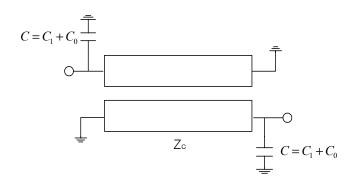

## 3.5 평형증폭기

정합 회로를 설계시에 부정합이 발생할 경우 입력과 출력의 VSWR과 이득을 감소시킨다. 이런 문제를 해결하기 위해 대표적으로 평형 증폭기가 사용되어 진다. 평형 증폭기를 사용할 경우 높은 안정성, 2배의 출력 파워, 한 쪽의 파손 시에도 사용 가능(인공 위성등의 고신뢰 시스템에서 신뢰성 향상)하다는 이점등이 있다.

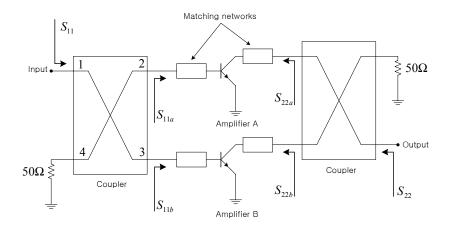

그림 3.2 평형 증폭기 구조 Fig. 3.2 Balanced amplifier configuration.

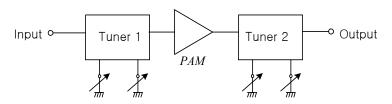

그림 3.2는 일반적인 평형 증폭기를 나타내는 그림으로 평형 증폭기의 원리는 다음과 같다.

$$[S] = \begin{bmatrix} 0 & \frac{e^{-j\pi/2}}{\sqrt{2}} & \frac{e^{-j\pi}}{\sqrt{2}} \\ \frac{e^{-j\pi/2}}{\sqrt{2}} & 0 & 0 \\ \frac{e^{-j\pi}}{\sqrt{2}} & 0 & 0 \end{bmatrix}$$

(3.16)

식 (3.16)은 포트 4가 50  $\Omega$ 에 종단되었을 때의 S파라미터를 나타내고 있다. 그림 3.2에서 포트 1에서의 입사파  $a_1(a_2=a_3=0)$ 일 때 , 포트 2와 3에서의 출력파는  $b_2=a_1e^{-j\pi/2}/\sqrt{2}$ 이고  $b_3=a_1e^{-j\pi}/\sqrt{2}$ 이다.

이 출력파는 똑같은 진폭과  $\pi/2$ 의 위상차를 가지고 있다. 즉 포트 2와 3로 전달되는 전력은  $|b_2|^2 = |b_3|^2 = |a_1|^2/2$ 로서 입력 전력에 1/2임을 나타내고 있다. 그리고 포트 4가  $Z_0 = 50$   $\Omega$ 에 종단되어 있을 때 포트 2와 포트 3에 증폭기가 연결된 경우  $S_{11a}$ 와  $S_{11b}$ 의 입력 반사계수를 가질 때, 반사 전압

$a_1 e^{-j\pi/2}/\sqrt{2}S_{11a}$ 와  $a_1 e^{-j\pi}/\sqrt{2}S_{11b}$ 가 포트 2와 3에 생성된다. 이 반사 전압이 포트 1으로 진행할 때 포트 1에서의 전체 반사 신호는 다음과 같다.

$$b_{1} = \frac{a_{1}}{2} e^{-j\pi} S_{11a} + \frac{a_{1}}{2} S_{11b} = \frac{a_{1}}{2} e^{-j\pi} (S_{11a} - S_{11b})$$

(3.17)

포트 1에서의  $S_{11}$ 은 식 (3.22)와 같다.

$$S_{11} = \frac{e^{-j\pi}}{2} (S_{11a} - S_{11b}) \tag{3.18}$$

그리고 다른 파라미터 역시 동일한 방법으로 표현하면, 다음과 같이 나타낼 수 있다.

$$S_{21} = \frac{e^{-j\pi/2}}{2} (S_{21a} + S_{21b}) \tag{3.19}$$

$$S_{12} = \frac{e^{-i\pi/2}}{2} (S_{12a} + S_{12b}) \tag{3.20}$$

$$S_{22} = \frac{e^{-j\pi}}{2} (S_{22a} - S_{22b}) \tag{3.21}$$

즉 두 개의 증폭기가 이상적으로 같을 경우  $S_{11}=0$ ,  $S_{22}=0$ 이 되고  $S_{21}$ 의 이득은 결합기의 한쪽에서 나오는 것과 같다[11].

# 제 4장 평형증폭기의 제작 및 측정

## 4.1 실험에 사용된 전력 증폭기의 특성

먼저 시뮬레이션 Tool은 ADS2001을 사용하여 설계하였고, 측정은 Agilent 사의 8753D network analyzer를 이용하여 측정하였다.

실험에 사용된 트랜지스터는 MRF 581로 모토로라에서 만든 고출력 트랜지스터로서 중심 주파수는 880 MHz이고, 동작 전류는 Ic=75 mA,  $I_b=500$   $\mu$ A, Vce=10 V이다. 본 실험에서는 높이는 0.5 mm, 유전율은 3.5인 테프론 기판을 사용하였다.

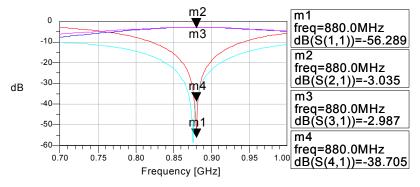

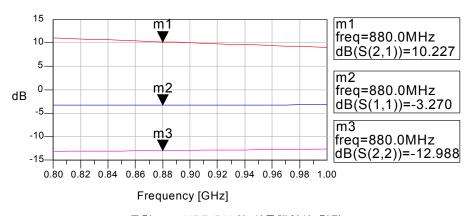

그림 4.1 MRF 581의 시뮬레이션 결과 Fig. 4.1 Simulated result of MRF 581.

그림 4.2 MRF 581 측정 결과 Fig 4.2 Measured result of MRF 581.

그림 4.1과 그림 4.2는 시뮬레이션 결과와 실제 측정결과로서 시뮬레이션 결 과와 측정치가 일치하는 것을 볼 수 있다. 그리고 결합기 제작시에 증폭기의 입·출력의 임피던스에 맞게 설계하기 위하여 그림 4.3과 같은 회로를 구성하 여 입력과 출력의 임피던스를 측정하였다.

그림 4.3 임피던스의 측정 회로도

Fig. 4.3 The optimal impedance measurement diagram.

그림에서처럼 Tuner를 이용하여 입력과 출력의 임피던스를 구하는 것은 Tuner가 스미스 도표의 전영역을 포함하기 때문이다. 먼저 Tuner 1을 이용하 여 최고 이득이 나오게 조절하고, 다음으로 Tuner 2를 조정하여 이득이 최고가 나오게 조절한다. 위의 같은 방법을 이용하여 실제 몇 번의 제작 측정결과 입 력과 출력 임피던스는 약 20 Q과 50 Q(오차는 약± 5 Q)으로 나타났다.

#### 4.2 제작 및 실험

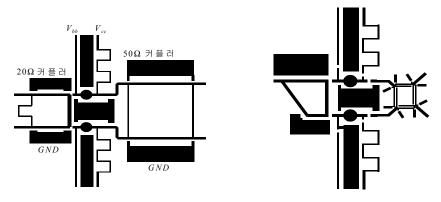

(a) 소형 결합기를 이용한 평형 증폭기 (b) 제안된 결합기를 이용한 평형 증폭기

그림 4.4 제작된 평형증폭기의 layout

Fig. 4.4 The layout of a fabricated balanced amplifier.

그림 4.4에서 (a)그림은 평형 증폭기의 실제 레이아웃(layout)이다. 앞단 결합기는 MRF 581의 입력 임피던스 20 2을 고려하여 제작하였고, 뒷단은 출력 임피던스를 고려하여 50 2으로 제작하였다. 다음은 제안된 평형 증폭기의 실제레이아웃(layout)은 그림 4.6에서 (b)와 같다. 평형 증폭기에서 앞단 결합기는 포트 4를 10 2으로 종단시키고, 20 2으로 임피던스가 변환되는 결합기를 제작하였고, 뒷단은 병렬 커플라인을 이용하여 임피던스 변화가 없는 결합기를 제작하였다.

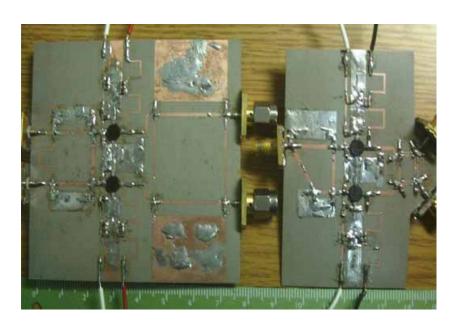

그림 4.5 제작된 평형증폭기의 사진 Fig. 4.5 The photograph of the balanced amplifier.

그림 4.5은 실제 제작된 평형 증폭기의 실물 사진을 나타내었다. 실물 사진에 서도 볼 수 있듯이 사진 왼쪽의 기존 소형화된 결합기보다 더욱 작은 크기를 구현하였다.

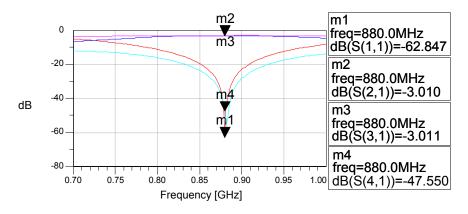

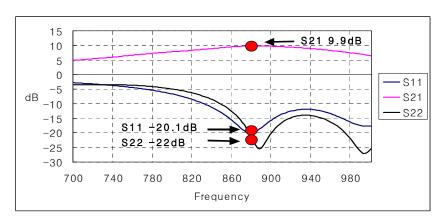

그림 4.6은 시뮬레이션 결과이고, 그림 4.7은 본 논문의 2.2절에서 측정된 결합기를 사용하여 평형증폭기를 설계하여 측정한 결과이다. 그리고 평형증폭기

의 정합회로는 병렬 커패시터 소자 하나만으로 정합회로 구성하였다. 이것은 결합기의 임피던스 변환에 의해 정합회로를 간단히 할 수 있는 장점 때문이다.

그림 4.6 평형증폭기의 이득 및 입출력 반사 손실의 시뮬레이션 결과 Fig. 4.6 Simulated gain and input · output reflection loss of balanced amplifier.

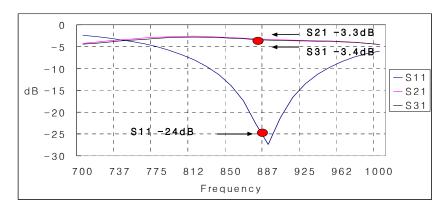

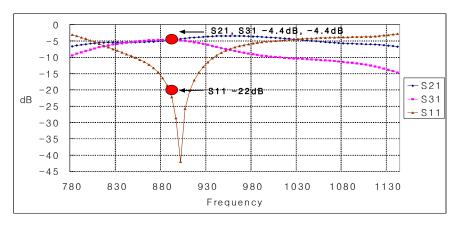

그림 4.7 평형 증폭기의 이득 및 입출력 반사 손실의 측정 결과

Fig. 4.7 Measured gain and input · output reflection loss of balanced amplifier.

그림 4.7에서 입력과 출력의 반사 손실이 개선되는 것을 볼 수 있었고, 입력과 출력의 VSWR 역시 1.4이하로 나타났다. 하지만 이득은 시뮬레이션 결과보다 특성이 나쁘게 나타났는데, 이득에서의 손실은 앞단과 뒷단의 결합기에의한 손실이 약 -2 dB 정도로 나타나는 것을 의미하는데 실험실에서 표준화된

공정이 힘들므로 만드는 과정에서 생기는 오차와 결합기 제작시 증폭기의 입력과 출력 임피던스에 정확하게 설계가 되지 않았음을 의미한다.

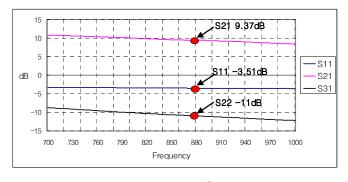

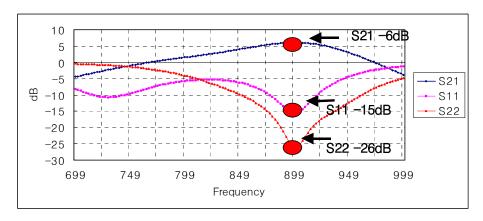

그림 4.8 평형 증폭기의 이득 및 입출력 반사 손실의 측정 결과 Fig. 4.8 Measured gain and input · output reflection loss of balanced amplifier.

그림 4.8은 본 논문의 2.3절과 2.4절에서 제안된 결합기를 이용하여 평형 증폭기를 제작하여 측정한 결과이다. 이득은 6 dB 로 나타났고, 입력과 출력의반사 계수는 각각 -15 dB와 -26 dB로 개선되는 것을 볼 수 있다. 이득에서 많은 손실이 발생하는데 이것은 결합기의 성능이 평형 증폭기의 성능에 영향을미치는데, 앞에서 측정한 결합 선로를 이용한 결합기의 손실이 평형 증폭기에반영된 것으로 사료된다. 그리고 모든 회로를 한 기판에 제작하는 과정에서 회로에서 발생하는 오차를 정확히 보정하기 힘든점 때문이다. 앞으로 MMIC같은표준화된 공정에서 제작될 경우 이런 손실을 작게 할 수 있으며, 기존의 결합기를 이용한 평형증폭기에 비해 크기와 성능면에서 개선된 직접회로 제작이 가능해진다.

# 제 5장 결 론

최근 이용량이 급증하고 있는 무선 통신의 비약적인 발전으로 무선통신 회로 및 부품을 직접화, 소형화, 안정화는 하는 것은 현대 무선 통신에서 중요한 관 심을 모으고 있다.

본 논문에서는 기존의 소형화된 결합기와 제안된 임의의 종단 임피던스를 갖는 결합기, 병렬 결합 선로를 이용한 결합기를 이용해 880 MHz에서 MRF 581 트랜지스터를 사용하여 평형증폭기를 설계하여 비교 분석하였다. 제안된임의의 종단 임피던스를 가지는 결합기의 경우 소형화된 결합기보다 크기를 더작게 만들 수 있었으며, 격리 포트의 임피던스를 조절해 각 선로의 길이를 보정할 수 있게 되어서 기존의 임피던스 변환 결합기의 비대칭에서 오는 크기의증가를 보정할 수 있는 장점도 가지고 있다. 또한 선로의 임피던스가 낮아짐으로 해서 고출력 평형증폭기의 임피던스 정합에 있어 임피던스의 조절이 용이해지는 장점이 있어서 반사특성이 우수한 평형증폭기 제작이 가능하다. 또한 병렬 결합 선로 결합기 이론을 접목하여 전통적인  $\lambda/4$  전송선의 길이의 10 %전후까지 줄일 수 있다.

실험을 통해 소형화된 결합기를 이용한 평형증폭기의 제작 및 측정 결과 크기는 기존의 분포 정수회로를 사용한 전통적인 결합기보다 약 95 %이상 작게설계되었다. 이득 및 입출력 반사 계수는 10 dB 이상 개선되었다.

향후 과제로는 결합기의 광대역화와 커패시터의 정확한 값의 구현을 위해 RFIC와 같은 표준화된 공정을 통해 정확한 설계가 요구되며 이런 공정으로 제작할 경우 기존의 결합기를 이용한 평형증폭기에 비해 크기와 성능면에서 개선된 회로 제작이 가능해진다.

# 참 고 문 헌

- [1] R.K. Gupta, and W.J. Getsing, "Quasi-lumped-element 3 and 4-port networks for MIC and MMIC applications," *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 409-411, 1984.

- [2] T. Hirota, A. Minakawa, and M. Muraguchi, "Reduced-Size Branch-Line and Rat-Race Hybrids for Uniplanar MMIC's," *IEEE Trans.* MTT, vol. 38, No. 3, pp. 53-56, March 1990.

- [3] M. Gillick, I.D. Robertson, J.S. Joshi, "Coplanar waveguide two-stage balanced MMIC amplifier using impedance-transforming lumped-distributed branchline couplers," *Microwaves, Antennas and Propagation, IEE Proceedings* vol. 141, Issue 4, pp. 241–245, Aug 1994.

- [4] H.R. Ahn, I. Wolff, I.-S. Chang, "Arbitrary termination impedances, arbitrary power divisions and small-sized ring hybrids," in: 1997 *IEEE MTT-S Internat. Microwave Symp. Digest.*, pp. 285–288, June 1997.

- [5] H.R. Ahn, I. Wolff, " 3dB branch-line hybrid terminated by arbitrary impedances," *Electronics Letters.*, vol. 34 pp. 1109–1110, may 1998.

- [6] G. Matthael, L. Young, E.M.T. Jones, *Microwave Filters, Impedance–Matching Networks, and Coupling Structures*, Artech House, pp. 218~228. 1980.

- [7] David M. Pozar, *Macrowave and RF Design of Wireless Systems*, Jhon Wiley & Sons, pp. 194~214, 2001.

- [8] R. Hajji, F. Beauregard, and F.M. Ghannouchi, "Multitone Power and Intermodulation Load-Pull Characterization of Microwave Transistors Suitable for Linear SSPAs Design". *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1093–1099, July 1997.

- [9] S.C. Cripps, "A theory for the Prediction of GaAs FET Load-Pull Power Contours," *IEEE MTT-S int. Microwave Symp. Digest., Boston*, MA, pp. 221–223, 1983.

- [10] J.B. Beyer, "MESFET Distributed Amplifier Design guidelines", *IEEE Trans Microwave Theory Tech.*, MTT-32, pp. 268-275, March 1984.

- [11] Guillermo Gonzalez, Microwave Transistor Amplifier Analysis and Design, 2nd Edition, Prentic Hall, pp. 212~333, 1997.

## 감사의 글

먼저 못난 저를 여기 있기까지 이끌어 주시고 도와주신 모든 분들에게 진심으로 감사의 마음을 전합니다.

본 논문이 있기까지 밤늦게까지 고생하시며 도와주신 저희 지도교수 강인호 교수님과 저의 논문 심사를 맡아 주시고 많은 관심을 귀울여 주신 김동일 교수님, 논문 마감까 지 고생하신 조형래 교수님께 감사드리며, 마지막까지 관심을 가지고 조언을 해주신 전파공학과 교수님들께 머리 숙여 감사드립니다.

정신적으로나 학문적으로 저에게 많은 귀감이 되셨던 교수이자 선배이신 마이크로파 실험실에 배대환 선배님, 손준형 선배님 그리고 늦깎이 선배 최동한 형에게도 감사 드 립니다. 그리고 술친구이자 같이 졸업하는 외형씨, 동우에게도 감사의 마음을 전하고, 마지막까지 학교에 남아 있는 동기 성준, 정원이와 고등학교 후배이지만 챙겨주지 못 한 철성이 우리 실험실에 동기이며 감사의 글에 "정말 고마운"이란 말을 넣어 달라는 사공 헌, 실험실 늦깎이 김정훈, 밤을 새워가며 모든 일을 같이 하며 생사 고락을 같이 한 내가 아끼는 후배 진산이와 재교에게도 감사에 마음을 전합니다. 다른 실험실에 윤 준씨 후배 태길이와 도연이 그 외 모든 실험실 선,후배님들에게 감사의 마음을 전합니다.

그리고 내가 힘들 때 옆에서 힘이 되어주었던 죽마고우 경득이랑 애 아버지가 되는 경록이와 그의 아내되는 현숙이에게도 감사하고, 고등학교부터 고스톱으로 우정을 쌓 아온 명신, 이름을 꼭 넣어 달라는 유리, 순자와 대학교 친구이지만 그 이상의 친구 태 웅이와 성민이 그리고 진우, 태현이 후배 현호와 여기에 이름이 있지 않은 많은 친구 들에게 정말 감사의 마음을 전하고 싶습니다.

마지막으로, 끝까지 옆에서 묵묵히 지켜봐준 건애와 정말 저를 여기까지 있게 해주신고마운 아버님, 어머님 그리고 동생 병화에게 고마운 마음을 전하고 싶습니다.

항상 정직하며 성실하게 살라는 부모님 말씀과 어려운 일이 있을 때 위의 고마운 분들을 생각하며 열심히 삶을 살도록 노력하겠습니다.