# 주파수합성기를 이용한 RF 송수신기의 개발에 관한 연구

A Study on the Development of RF Transceiver Using PLL

姜 東 均 <sup>1)</sup> 金 東 一 <sup>2)</sup>

Dong - kyun kang , Dong IL Kim

#### **Abstract**

The wireless local loop system developed from the mobile communication technology as core equipment of the future radio communication technology can provide high speed data transmission services and it is expected to put into commercial services using W-CDMA in domestic region in 1999. The subscribers and base stations at a commercial scale level are being designed and manufactured on the basis of TTA recommendation (W-CDMA common air interface for WLL systems using the frequency range of 2.3GHz and it is also planned to develop the common air interface for WLL compatable with the domestic radio environment through—continuous tests between test-bed base stations and subscribers.

The dissertation deals with the research work involved in the development of an RF transceiver which was designed and realized. The common air interface and the design specifications as follows. First, modulation, demodulation and frequency synthesiser on the wide bandwidth could be achieved. Second, considering complicated radio environment, spurious characteristics which can transceive radio waves within the allocated bandwidth is emphasized. Third, considering fading from the radio environment, automatic gain control

<sup>1)</sup> 안국해양대학교 전자통신공학과 박사과정 무선시스템회로 전공

<sup>2)</sup> 한국해양대학교 전화공학과 교수

characteristics could be realized. And referring to the system requirements of DACOM and the data from the existing subscribers, transceiver specifications were established.

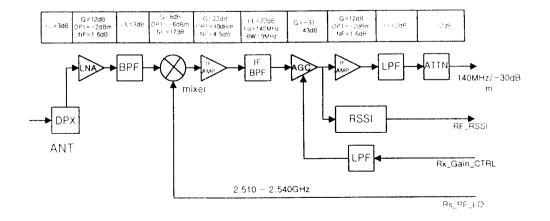

After designing the framework, the intermediate frequencies and the frequency of local oscillator have been decided at the design stage of the receiver. After designing each block and allocating the gain and the loss corresponded to the receiver sensitivity and the intercept point at each block, the power burget has been audited, suitable devices selected and then the circuits designed. Especially I selected the size of the devices and the devices, themselves, after consideration of the subscribers characteristics and the operating voltage.

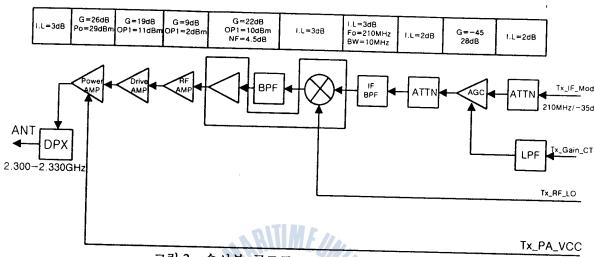

The intermediate frequency of the transmitter has been established according to the frequency arrangement decided at the receiver and then each block has been designed. After then we allocated the gain and the loss to each block and selected suitable devices of the transmitter. Especially the output power, the transform efficiency, and the linearity were taken into account during the design of the power amplifier.

A computer simulation has been carried out to verify the conformance of the transceiver design. The software, HP EEsof is used, VSWR and gain have been performed for the receiver index, noise and gain and power for the transmitter. The Library of devices which is not provided by the program packages is designed by carrying out block tuning. The results of the computer simulation accomplished by the insertion of s-parameter have exhibited an excellent agreement with the design value.

The programmable counter and the loop filter are designed by using the PLL chip with the dual modulus prescale and charge pomp in the course of designing the frequency synthesizer. A third order passive filter attached with a reference suppression filter is used for the design of the loop filter and the value of the loop filter is selected via the decision of the open loop bandwidth and the phase margin for the benefit of superior noise characteristics.

The transceiver was made on a 4 layer FR4 PCB with reference to the application circuit provided by the device manufacturer. The matching circuit has been designed by tuning when designing the power amplifier of transmitter and the low noise amplifier of receiver.

From the test result, it was known that the transceiver exhibited superior performance enough to handle the received signal level variation caused by fading. It also exhibited superior characteristics over the spurious radiation in the range of the inband and outband because the range of automatic gain control for receiving has a gain of 60dB for transceiving. The maximum transmitting power was 15.6dBm and spurious rariation was -17dBc at the point separated 5MHz from the transmission band and -26dBc at the point at the point separated 10MHz from the transmission band. Power control of the closed loop and the frequency precision demonstrated stable characteristics.

The W-CDMA RF transceiver using frequency synthesis which is developed in this dissertation will be used for the common air interface test among the base station and subscribers of the WLL system and it is expected to contribute to the development of the domestic standards for business services using W-CDMA for the first time in the world. If devices operated on wide band will be developed consistantly in the future, it is expected that many more superior transceivers can be developed once. The minimal performance specifications of the subscribers based on the final common air interface are established optimized values of RF parameters based on these specifications will be determined and from that it is expected that the development of commercial level transceivers will be in the near future.

#### 1.서론

본 논문에서는 WLL 국내 무선접속규격을 개발하기위한 RF 단 단말기를 설계 제작 구현하였으며, 차후 이 단말기를 통해 국내 WLL 무선접속규격을 결정하는데 사용할 예정이다. 따라서 이러한 목적을 달성하기 위해 주파수 안정도 특성을 가진 최적의고주파(RF; Radio Frequency)송수신부의 설계 및 제작에 관한 연구가 필요한 실정이다. 그러므로 본 논문에서는 광대역 코드분할 다원접속방식을 이용한 WLL 단말장치에 사용할 수 있는 RF 송수신기를 설계 제작 하였으며, 그 성능을 상용 소프트웨어를 이용하여 시뮬레이션 결과와 비교 하였다. 여기에서 수신부의 성능평가 요소로서 수신감도, 수신자동이득제어(AGC; Automatic Gain Control)범위, 전도성 스퓨리어스 방사둥을 기준하였으며, 송신부에서는 최대 송신출력, 전도성 스퓨리어스, 폐루프 전력제어범위, 주파수 정밀도 등을 시스템의 주된 설계규격으로 설정하여 제작된 주파수합성방식의 광대역 송수신기의 성능을 평가하였다

#### 2. 본 론

본 연구에서는 2.3GHz 대용 PLL을 이용한 RF 송수신기를 개발하는데 제 2 장에서는 단말기의 RF 설계규격을 설명하고 최종규격을 설정하였다. 제 3, 4 장 송수신부 설계 부분에서는 구조설계와 회로설계를 하였으며 사용한 소자특성등을 기술하였다. 제 5 장에서는 주파수 합성부 설계부분으로 기본적인 PLL 동작원리등을 언급하며 선정한소자에 따른 카운터 및 루프필터 회로설계등을 설명하였으며 제 6 장에서는 송수신부에 대한 시뮬레이션으로서 설계치와 시뮬레이션 결과치를 비교확인한다. 마지막으로 제 7 장에서는 제작 및 실험결과로서 결론을 맺는다.

### 2.1 설계규격

| हि           | 무                                       | 설 계 규 격            | 비 고         |

|--------------|-----------------------------------------|--------------------|-------------|

| 구 과 수        | 송 신                                     | 2300~2330 MHz      |             |

| 동작범위         | 수 신                                     | 2370~2400 MHz      |             |

| 다 풀 백 소      | 방 식                                     | FDD                |             |

|              | 간 격                                     | 70 MHz             |             |

| RF 채 널 대 역 폭 |                                         | 10 MHz             |             |

| 변 복 조 방 식    |                                         | QPSK               |             |

| 데이타전송속도      |                                         | 8.192 Mcps         |             |

| 안 테 나        |                                         | 송 수 신 공 용          |             |

| 수 신 감 도      |                                         | -113 dBm           |             |

| 수신 자동이득제어 범위 |                                         | 60 dB 이상           |             |

| 수신전도성        | 송 신 대 역                                 | -60 dBc/30 kHz 이하  |             |

| 스퓨리어스        | 수 신 대 역                                 | -80 dBc/30 kHz 이하  |             |

| 방 사          | 대 역 외                                   | -47 dBc/30 kHz ০ ক |             |

| 송신 저 대 출 력   |                                         | 150 mW             |             |

| 송신전도성        | 송 신 대 역                                 | -13 dBc/30 kHz া ক |             |

| 스퓨리어스        | 수 신 대 역                                 | -80 dBc/30 kHz া ই |             |

| 방 사          | 1 1 51                                  | 00,450,50 11,21    |             |

| 폐루프 전력제어 범위  |                                         | 24 dB              |             |

| 주파수정밀도       |                                         | ±2.5 ppm           | @System:기지국 |

|              | 110000000000000000000000000000000000000 | @System: ± 0.1 ppm |             |

# 2.2 수신부 설계

그림 1 수신부 구조도

# 2.3 송신부 설계

그림 2 송신부 구조도

### 3. 결 론

본 논문에서는 주파수합성방식의 W-CDMA 용 RF 송수신기를 설계 제작하였다. 이 W-CDMA RF 송수신기는 무선가입자망 장치의 무선접속규격을 개발하기 위해 제작한 것으로 개발규격은 2.3GHz 대역의 WLL 무선접속 시험을할 수 있도록 송수신기 규격을 설정하였으며 특히 타주파수대역에 간섭을 일으킬수 있는 스퓨리어스 방사규격은 최대한 억제 할 수 있도록 설정하였다. 그외 대부분은 기존 IS-95 규격을 준용하고 있는 셀룰러 및 PCS 규격을 참조하여 설정하였다.

송수신부 설계에서는 기본구조 및 주파수 배치를 하였으며 블록설계 후 각 블록에 대해 하드웨어 규격을 설정하였다. 이 결과를 토대로 상용 소프트웨어인 CDS로 각송수신부에 대한 버짓 및 소신호, 대신호 해석을 하여 설계치와 비교하여 검증하였으며, 각 회로설계 및 제작에서는 기존 상용부품과 여파기는 주문제작하여 회로를 구성하였다. 수동회로들은 터치스톤 소프트웨어를 활용하여 설계및 제작을 하였다.

시험결과 수신자동이득 조정범위가 60 dB 정도의 이득을 가지고 있어 페이딩에 따른 수신신호 레벨변동에 대해 충분히 대응할 수 있게 하였으며, 스퓨리어스 방 사는 송수신대역 및 대역외 범위에서 깨끗한 특성을 나타나는 것을 확인하였다. 송

선단에서는 최대 15.6 dBm 정도의 송신출력 특성을 나타내었으며, 스퓨리어스 방사에서는 송신대역에서 5 MHz 이격된 지점에서 -17 dBc, 10 MHz, 이격지점에서는 -26 dBc 정도의 특성이 나타내었다. 수신대역에서는 -80.6 dBc 정도로 나타나 우수한 특성이 나타나도록 제작되었다. 그 외 폐루프 전력제어 및 주파수 정밀도도 안정한 특성을 나타내었다.

본 논문에서 개발된 W-CDMA RF 송수신기를 이용하여 무선 가입자망 시스템의 기 지국 과 단말기간 무선접속 시험에 활용하여 세계최초의 W-CDMA를 통한 상용 서 비스를 할 수 있는 국내 표준규칙을 마련하는 데 기여할 것으로 기대된다. 차후 관 런 광대역용 부품개발이 지속적으로 이루어지면 보다 우수한 송수신기 개발이 가능 알 것으로 예상된다. 또한 무선접속규칙에 의한 단말기의 최소성능규칙이 확정된다 면 이규칙을 바탕으로 보다 최적화된 RF 파라미타 설정이 이루어져 상용수준의 송 수산기 개발이 가능할 것으로 사료된다.

### 참 고 문 헌

- 1945

- [1] 박항구. "이동통신의 발전방향"는 97 년 4 월 전자공학회자 제 24 권 제 4 호. pp399-415, 1997.

- [2] 테이콤. "무선가입자망(WLL)시스템 요구사항(안)", 1996.

- [3] ITA. "2.3GHz 대역의 WLL 시스템을 위한 광대역 CDMA 무선접속 규격 표준", 1997.

- [4] 김남수. "DS/CDMA 이동국 RF 수신시스템의 설계에 관한 연구", 한국통신 학회. 95-4 Vol.20, No4, 1995.

- [5] 정영준외 3 명. "Wideband CDMA PCS 기지국용 송수신시 설계 및 구현". 한국전자파학회 논문지, 제 8 권 제 1 호, pp61-72, 1997.02.

- [6] Qualcomm, "The CDMA Network Engineering Handbook" Volume 1,2,1993.

- [7] P. Vizmuller, "RF Design Guide", Artech House, 1995.

- [8] S. J. Erst, "Receiving System Design", Artech House, 1984.

- [9] 임승하의 "전자통신기기" PP115-134, 도서출판 광명, 1997

- [10] Lawrence E. Larson, "RF and Microwave Circuit Design For Wireless Communications", Artech House, 1996.

- [11] 과학기술정보 연구소, "전자통신기기의 RF 회로설계 기술 및 활용", 1997.

- [12]이재신의 "이동통신용 고주파 필터기술현황", '94 국내의 한국과학기술자 학술회의 추계 Workshop 이동통신분과 PRE-PRINTS, 한국과학기술단체 총 연합회, PP85-94, 1994.

- [13] D.M. Pozar," Microwave Enginerring", Addison-Wesley, 1990.

- [14] Robert E. Collin "Foundation for microwave engineening". McGraw-Hill, 2<sup>nd</sup> edition, pp397-403, 1992.

- [15]강동균,김동일. "Test-bed 용 WLL 단말기 RF 수신기 설계 및 제작". 한국 통신학회. 추계합동학술논문발표회. '97.12.6

- [16] G. A. Brees, "Filter Handbook Vilume 2-Design", RF Design Collection, PP66-78, 1992.

- [10] Mini-circuit, "RF/IF Designer's Handbooks Section1". PP1-29, 1992/3.

- [17] John L.B. Walker, "High-Power GaAsFET Amplifier", Artech House, 1984.

- [18] G.Gonzalez, "Microwave Transister Amplifier Analyzer and Design", Printice-Hill Inc, PP125-133, 1994

- [19] 세운, "PLL 응용회로", pp13-125,1993

- [20] Dan H. Wolaver, "Phase Locked Loop Design", Prentice Hall, 1991

- [21] Willam O.Keese, "An Analyzer and Performance Evaluation a passive filter design technique for charge pump phase locked loop" RF EXPO, pp36-41, 1995.

- [22] Gray A.Breed, "Frequency Synthesis Handbook, Caridift Publishing Company, pp4-22, 1992.

- [23] National Semiconductor "Charge-pump Phase-Lock loop Filter Design" Application Note, 1991.

- [24] Qualcomm "Synthesizer Products Data Book", 1996.

- [25] Hewlett Packard Co, HP-Eesof Microwave & RF System Design, 1994.

- [26] 문영찬외 2명, "PCS 기지국 RF 송수신부의 설계 및 성능평가", Telecommunications REVIEW Vol.11, No11, 1995.